استفاده از یک مشخصات عمومی

مدار حاصل شکل ۱۵ محدود به چهار بیت است. مدار مشابهی که بتواند ۳۲ بیت را جمع کند، نیاز به نمونه سازی ۳۲ مدار تمام جمع کننده درVerilog دارد. از دید طراح مدار، در پیاده سازی اینچنین مداری که هر اندازهی دلخواهی میتواند داشته باشد، بهتر است که برای مشخص نمودن اندازهی آن از یک پارامتر استفاده شود.

با استفاده از Verilog میتوان یکسری پارامترهای عمومی تعریف کرد و به آن ها مقدارهایی دلخواه نسبت داد. برای مثال یک بردار n بیتی (که در آن مقدار n مشخص است) بصورت W[n-1:0] نمایش داده میشود. اگر n در Verilog بصورت زیر تعریف شود،

parameter n = 4;

پس محدودهی بیتهای W برابر [3:0] است.

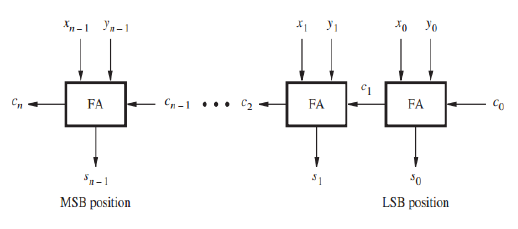

مدار جمع کنندهی شکل ۱۶ را میتوان با استفاده از عبارات منطقی توصیف کرد.

شکل ۱۶

شکل ۱۶

Sk = Xk ⨁ Yk ⨁ Ck

Ck+1 = Xk Yk + Xk Ck + Yk Ck

بدین ترتیب، بجای نمونه سازی مدارهای تمام جمع کننده، میتوان از این عبارات برای توصیف جمع کنندهی مورد نظر استفاده نمود.

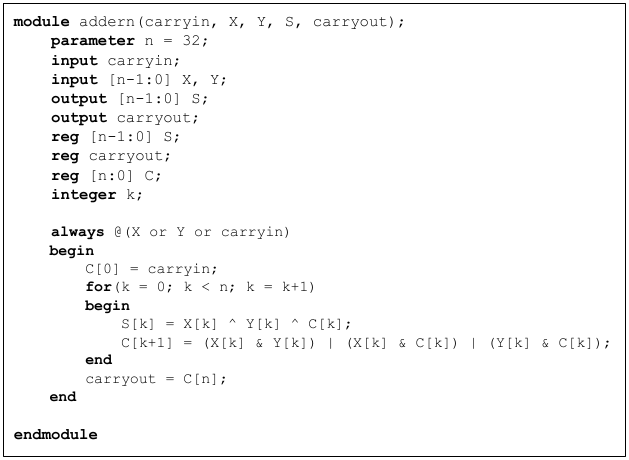

در شکل ۱۷ توصیف Verilog یک جمع کنندهی n بیتی نشان داده شده است. ورودیهای X و Y و خروجی S بصورت بردارهای n بیتی تعریف شدهاند. برای ساده سازی استفاده از سیگنال های نقلی در مدار، یک بردار n+1 بیتی بنام C تعریف شده است. بیت C[0] به عنوان بیت ورودی نقلی برای LSB و C[n] بیت نقلی برای MSB در نظر گرفته شدهاند(C[0] = carryin و C[n] = carryout).

برای مشخص کردن ساختار تکراری مدار جمع کننده، در کد شکل ۱۷ از عبارت for استفاده شده است. همانند قالب دستورات شرطی if-else که در بخشهای قبل توضیح داده شده بود، دستور for نیز یک قالب رویهای دارد که باید درون یک بلوک always قرار گیرد. در این حالت نیز، هر سیگنال که درون بلوک always مقدار دهی میشود، تا زمانی که متغیرهای حساسیت بلوک always تغییر نکنند، باید مقدار خود را حفظ کنند. چنین سیگنال هایی باید بصورت reg تعریف شوند. در برنامهی Verilog شکل ۱۷ سیگنالهای carryout، S و C از نوع reg تعریف شدهاند و متغیرهای لیست حساسیت سیگنال های X، Y و carryin هستند.

شکل ۱۷

شکل ۱۷

در مثال ذکر شده، حلقهی for شامل دو عبارت begin و end میباشد. در داخل این عبارات، با استفاده متغیر موجود در حلقه، توابع sum و carry هر طبقه از مدار جمع کننده تعریف شدهاند. محدودهی متغیر k بین 0 تا n-1 میباشد و در هر بار تکرار حلقه، یک واحد به مقدار آن اضافه میشود. k بصورت یک عدد صحیح تعریف میشود و تعداد تکرار حلقهی for را معین میکند. برای مثال اگر مقدار k برابر 2 در نظر گرفته شود، حلقهیforبرابر با چهار عبارت زیر میگردد:

S[0] = X[0] ^ Y[0] ^ C[0];

C[1] = (X[0] & Y[0]) | (X[0] & C[0]) | (Y[0] & C[0]);

S[1] = X[1] ^ Y[1] ^ C[1];

C[2] = (X[1] & Y[1]) | (X[1] & C[1]) | (Y[1] & C[1]);

در کد Verilog شکل ۱۷ که مقدار پارامتر n برابر 32 در نظر گرفته شده است، یک جمع کنندهی ۳۲ بیتی پیاده سازی شده است.